Logic

对于3D NAND“节点”,可以轻松地根据物理层数进行定义,对于DRAM节点一般采用有源区的半节距,而逻辑节点几乎是公司营销人员称之为多少就是多少。

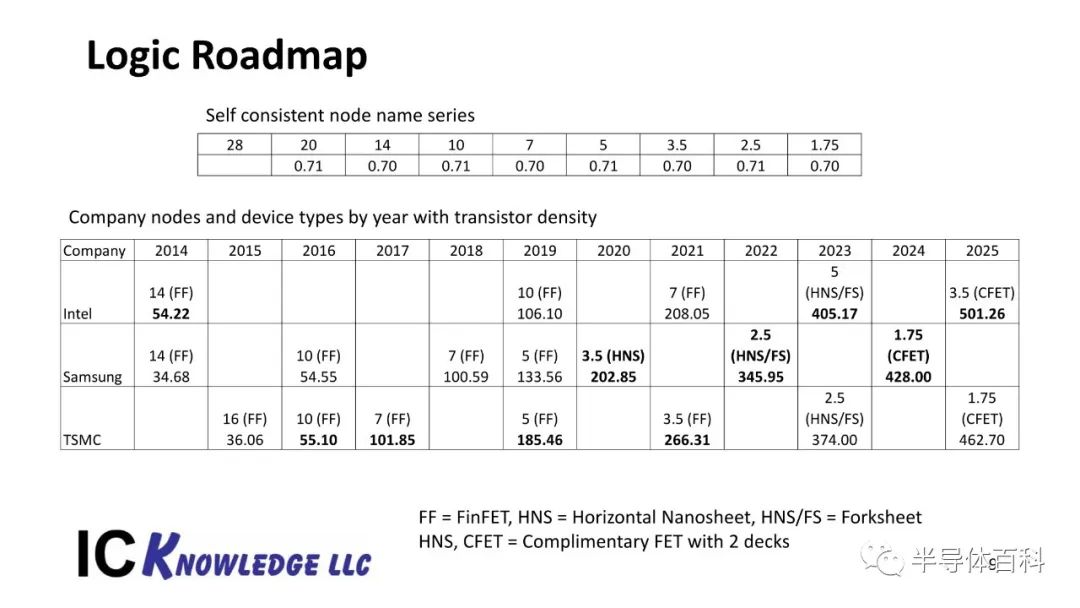

由于FinFET是3D结构,因此某些人认为当前的FinFET前沿工艺是3D,但在本次讨论中,我们认为3D是指器件堆叠,即允许堆叠多个有源层以创建器件堆叠的情况。在这种情况下,一旦采用CFET,3D逻辑器件将真正出现。图7列出了追求最新技术的3家公司的节点路线图。

图7.逻辑路线图。

由于英特尔与代工厂之间的分裂,此图中的节点比较变得复杂。英特尔遵循经典的节点名称,即45nm,32nm,22nm,14nm,而代工厂遵循的是“新”节点名称,分别为40nm,28nm,20nm,14nm。此外,英特尔在每个节点上微缩更多,因此Intel 14nm的密度与代工厂10nm类似,Intel 10nm的密度与代工厂7nm类似。

在图的顶部,我概述了基于交替的0.71和0.70倍微缩得到的节点名称系列。在图的底部,我按公司和年份列出了每个节点的晶体管密度。如前所述,晶体管密度是基于NAND和Flipflop单元的权重计算的。括号中每个节点的旁边是FF(FinFET),HNS(水平纳米片),HNS / FS(Forksheet,基于Imec的工作来提高密度)和CFET(互补堆叠的FET,其中nFET和pFET是垂直堆叠)。CFET量产之时,就是逻辑微缩从基于单层的微缩成为真正的3D解决方案之日,原则上CFET可以通过添加更多层来继续进行微缩。

图中粗体表示领先的密度或技术。2014年,英特尔凭借其14纳米工艺在密度上取得了领先地位。台积电在2016年以10纳米制程占据密度领先地位,并在2017年以7纳米制程保持领先地位。台积电和三星在7nm处的密度相似,但要达到5nm,台积电的微缩率要比三星大得多,2019年,台积电以其5nm技术保持工艺密度领先。如果三星在2020年实现HNS技术(我们称之为3.5纳米节点),那么他们可能会在密度上领先,并成为第一家制造HNS的公司。在2021年,TSMC的3.5纳米节点(我们称之为)可能会帮助他们返回到密度领先位置。如果英特尔能够实现他们通常目标的那种两年一次微缩的速度,我们相信他们可以在2023年在采用5纳米工艺时重新取得密度方面的领先。

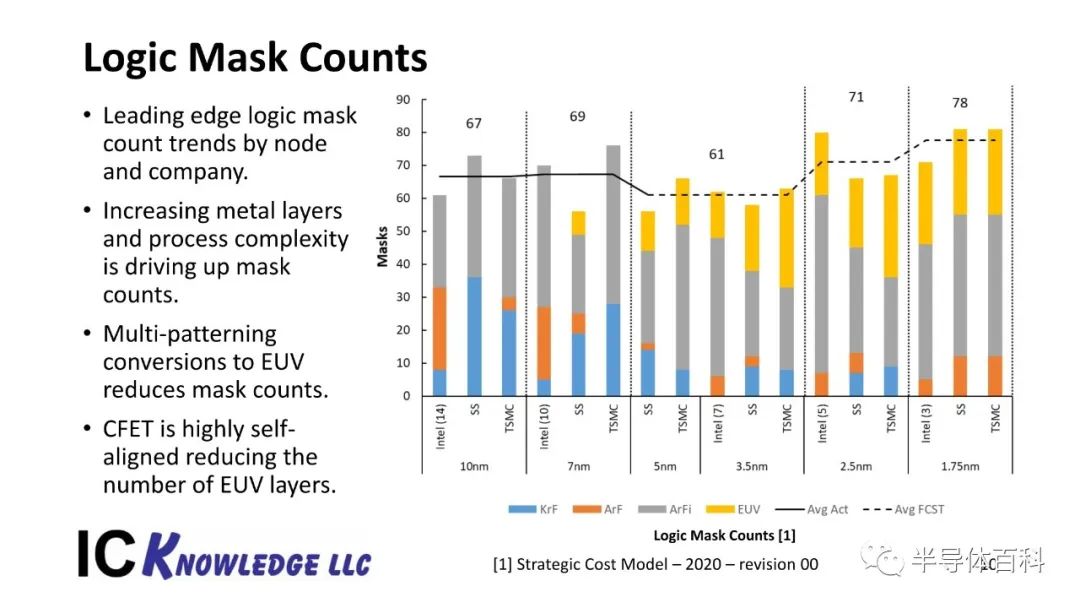

图8给出了这些逻辑制程的掩模数量。EUV的引入减少了掩模数,如果没有EUV,我们可能会在此图表上看到100个以上的掩模。正如我们对NAND掩膜计数图所做的那样,虚线是平均掩膜数。我们还基于“相似”密度对工艺进行了分组,例如,将Intel 14nm与代工厂10nm工艺结合在一起,将Intel 10nm与代工厂7nm工艺结合在一起。

图8逻辑制程掩模数趋势。