结果与讨论

首先,在测量电路板的板电容时没有使用DUT。图4所示电路板的测量条件是16 fF电容且没有DUT。这是一个相当小的电容,可以忽略不计,因为通常CDM的预期值为几百至几千fF。

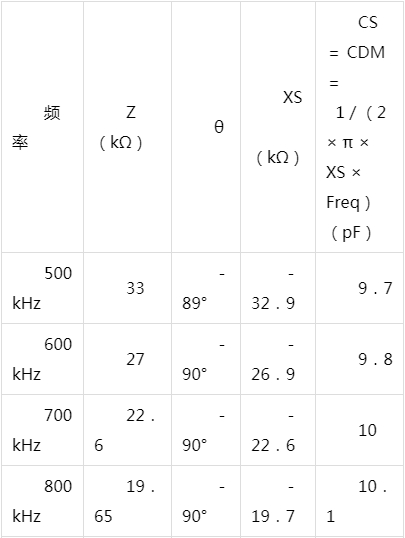

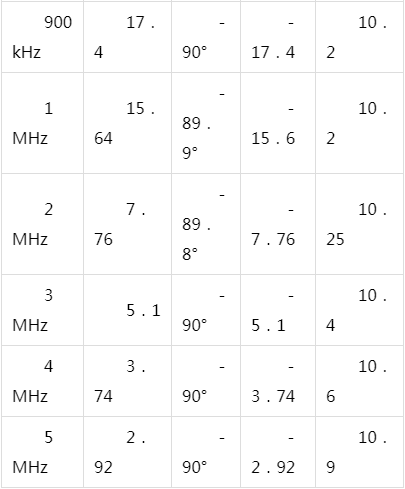

Most JFET and CMOS input op amps were measurable using this new CDM measurement使用这种新的CDM测量技术,可以测量大多数JFET和CMOS输入型运算放大器。为了说明该方法,以测量低噪声精度JFET运算放大器LT1792为例。下表列出了在一定频率范围内的阻抗(Z)、相位角(θ)、电抗XS和CDM的计算值。当相位角为-90°时,阻抗表现为纯容性。

表1.电源为±15 V时,LT1792在不同频率下的阻抗测量

上述表1给出了在500 kHz至5 MHz频率范围内的测量结果。在该频率范围内的相位接近于纯容性(相位角为-89°至-90°)。同时,电抗XS决定了总输入阻抗,即Z≈XS。CDM的计算平均值约为10.2 pF。最高测量频率为5 MHz,因为该器件带宽仅可达5.6 MHz。更低频率下的结果变得非相干。推测这是由于运算放大器的行为使输出电压降低,CDM电流迅速消减,同时XS阻抗在低频时变大。

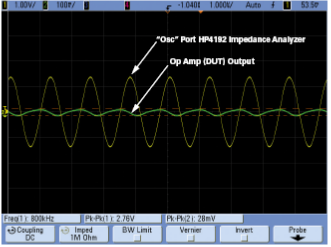

还应在每个阶跃频率处检查运算放大器的输出,以确保它不会被阻抗分析仪产生的信号过驱。来自HP4192A的该信号的幅度可在0.1 V至1.1 V范围内调节,这刚好足以在运算放大器的输出中产生摆动,并使反相输入引脚中的电压电平略微发生变动。图5显示了频率为800 kHz时,运算放大器输出端的峰峰值无失真信号(绿色信号)为28 mV。2.76 V峰峰值幅度(1 V rms)的黄色信号是直接从分析仪的振荡输出端口探测得的。公平起见,可以任意决定不允许输出失真,不论是对DUT还是对HP4192A检波器。尽管该设置相对来说并不受探头效应的影响,但在获取阻抗和相位的实际数据时已经将探头移除。

图5.在HP4192A“Osc”输出端口和运算放大器输出引脚探测到的输出。

我们进行了在不同电源电压下测量CDM的测试。CDM对电源和共模电压的依赖性会随运算放大器的不同而有所不同;不同的拓扑和晶体管类型预计会导致高压电源和低压电源不同的结寄生效应。表2给出了电源稳定在±5 V范围内LT1792的结果。CDM的测量平均值为9.2 pF,与采用±15 V电源时的结果10 pF相当接近。因此,可以得出结论,LT1792的CDM不会随电源电压的改变而发生显著变化。这与其CCM形成了鲜明的对比,后者会随电源电压发生显著变化。