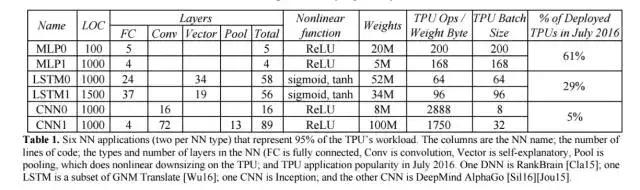

表 1:6 种神经网络应用(每种神经网络类型各 2 种)占据了 TPU 负载的 95%。表中的列依次是各种神经网络、代码的行数、神经网络中层的类型和数量(FC 是全连接层、Conv 是卷积层,Vector 是向量层,Pool 是池化层)以及 TPU 在 2016 年 7 月的应用普及程度。RankBrain [Cla15] 使用了 DNN,谷歌神经机器翻译 [Wu16] 中用到了 LSTM,Inception 用到了 CNN,DeepMind AlphaGo [Sil16][Jou15] 也用到了 CNN。

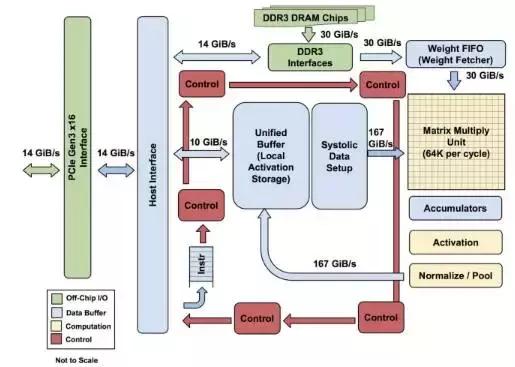

图 1:TPU 各模块的框图。主要计算部分是右上方的黄色矩阵乘法单元。其输入是蓝色的「权重 FIFO」和蓝色的统一缓存(Unified Buffer(UB));输出是蓝色的累加器(Accumulators(Acc))。黄色的激活(Activation)单元在Acc中执行流向UB的非线性函数。

图 2:TPU 芯片布局图。阴影同图 1。蓝色的数据缓存占芯片的 37%。黄色的计算是 30%。绿色的I/O 是 10%。红色的控制只有 2%。CPU 或 GPU 中的控制部分则要大很多(并且非常难以设计)。

图3:TPU印制电路板。可以插入服务器 SATA 盘的卡槽,但是该卡使用了 PCIe Gen3 x16 接口。

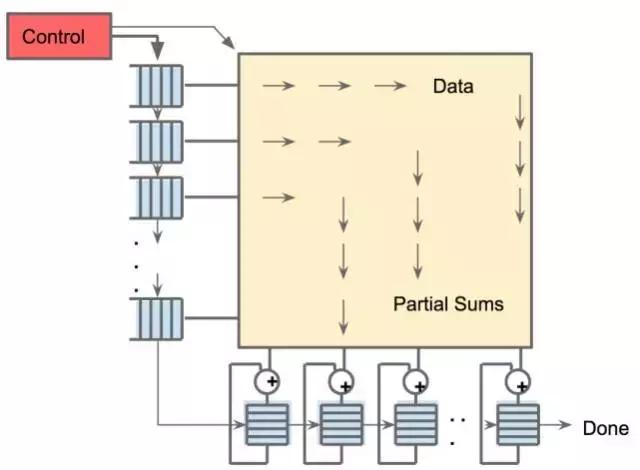

图4:矩阵乘法单元的 systolic 数据流。软件具有每次读取 256B 输入的错觉,同时它们会立即更新 256 个累加器 RAM 中其中每一个的某个位置。