4.2.2、多功能 / 低功耗集成电路技术

在半导体外延材料技术和微波单片集成电路工艺不断进步的推动下 , 微波单片集成电路逐渐向多功能方向发展 , 由于多功能芯片的不同功能电路之间的互连已在内部完成 , 焊点数量大大减少 , 可大幅度缩减芯片体积 , 降低成本 , 提高集成一致性和可靠性 . 例如微波收发多功能芯片可以将放大器、移相器、开关、衰减器等集成在一个芯片内 , 替代传统单功能芯片 . 由于多功能芯片的制造大多还没有专门的工艺平台 , 对于发射功率较小的情况 , 采用低噪声工艺实现 , 而功率较大时可采用功率工艺实现 ,所以接收或发射性能可能不能同时达到最佳状态 , 接收和发射链路的设计要素常常彼此冲突 , 因此在接收和发射性能平衡兼顾下 , 进行最优化设计是研究难点 。

低功耗集成电路的实质就是在集成电路的基础上 , 将整个电路系统的能耗降至最低 , 需要解决高K/ 金属栅技术、高迁移率沟道材料和超低亚阈值斜率器件等关键技术 , 而要想实现超低功耗集成电路 ,就需要从电路材料的选择、内部元件排列、电源硬件设计 , 以及系统能耗的控制等技术方面进行研究 。

4.2.3、智能控制集成电路技术

以天线阵列微系统体系架构需求为导向 , 基于软件可定义、硬件可重构的要求 , 开展基于 IP 模块的 SOC, 专用集成电路 (application specific integrated circuits, ASIC) 等多功能芯片研究和设计 , 突破IP 核复用技术、低功耗设计技术、可测试性技术等 . 同时根据天线阵列微系统微小尺度下多物理量耦合、多功能集成等特点 , 开展适配的软件算法的研究 , 重点解决天线阵列微系统软硬件协同设计的难题 . 围绕天线阵列微系统的功能增强和异构工艺适配开展芯片设计研究 , 优化控制策略 , 实现智能数字控制 , 降低系统功耗 , 突破海量数据实时处理、超高频、超高速和超大容量数据通信 , 以及高效热能量传递的技术瓶颈 , 并完善内部辅助功能和保护功能 , 实现接口标准化 , 提高天线阵列微系统硬件和软件的整体适用性和兼容性 。

4.3、多物理场匹配混合集成技术

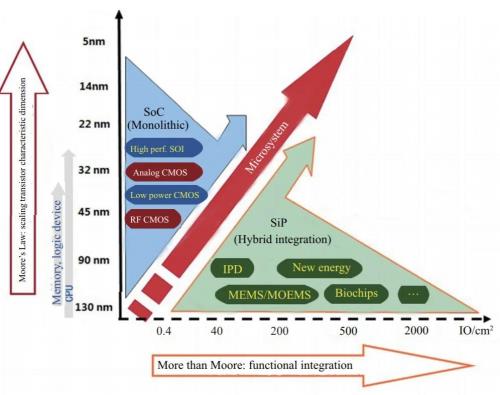

混合集成电路 (hybrid integrated circuit, HIC) 技术是采用厚 / 薄膜技术、微组装技术和封装技术将半导体芯片、无源元件等集成于一体来实现既定功能和性能 , 是实现天线阵列微系统的重要途径之一 . 图 8 是单片集成和混合集成关系示意图 , 单片集成是永恒的追求 , 混合集成是单片集成的二次集成 . 混合集成技术涉及到一个复杂的多层次多专业的技术体系 , 可以分为架构设计技术、多层互连基板技术、微互连技术、高气密性封装技术 , 以及可靠性评估与应用等一系列的基础理论、制造实践和应用技术 。

图 8 (网络版彩图) 混合集成与单片集成

多物理场匹配混合集成技术研究是天线阵列微系统小型化、轻量化、高密度、多功能的需求 , 基于电、光、磁、力等多物理场维度下的混合集成前沿性共性技术研究 , 重点突破 2.5D/3D 垂直互连、三维异质异构微组装和高密度异质多层基板等技术 , 解决天线阵列微系统中电磁兼容、高速信号传输与串扰、热管理、应力匹配、光电干涉等技术难题 。

混合集成技术的演进经历过四大变革 , 即通孔插装技术向表面安装技术的变革 , 周边互连到面阵互连的变革 , 单芯片向多芯片的变革 , 二维结构向三维结构的变革 . 正是这些变革使许多新型混合集成技术不断涌现 , 组装效率不断提高 , 推动混合集成电路向 “ 四高一小一轻 ” 方向不断发展 . “ 四高 ” 是高组装密度、高频、高功率密度、高可靠 ; “ 一小 ” 是体积更小 ; “ 一轻 ” 是重量减轻 。

4.3.1、2.5D/3D 垂直互连技术

2.5D/3D 垂直互连技术基于多学科多专业 , 融合了系统设计和微纳集成工艺 , 以实现不同材料、不同结构、不同工艺、不同功能元器件的三维异构集成 , 是以突破摩尔定律极限为目的, 重点解决天线阵列微系统内部高速、高频、大功率传输下的超高密度互连难题 . 2.5D/3D 互连通过基材过孔金属化垂直互连技术和凸点技术进行电气垂直互连 . 通过研究各种复合材料导体及介质对复杂信号的传输与屏蔽适应性和匹配性影响 , 解决微系统中可能出现的串扰、延迟、能耗等难点 . 同时 , 在工艺研究时 , 充分考虑热力学和电性能的参数匹配 , 避免不同材料之间的热失配和机械应力 。

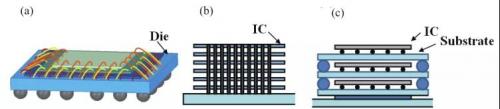

代表性的叠层型 3D 封装可以是裸芯片的叠堆 , MCM 的叠层甚至还可以是晶圆片的堆积 . 3D 先进封装典型结构如图 9 所示 . 3D-MCM 可以将不同工艺类型的芯片 ( 如模拟、数字和射频等功能芯片 ) 在单一封装结构内实现混合信号的集成化 , 在满足天线阵列微系统模块机械性能要求 , 以及在模块尺寸、重量及功耗极端受限的情况下 , 通过对多功能电路转接板厚度进行最优化设计 , 可以减小天线阵列微系统封装体的厚度 , 并进一步提高集成密度 . 3D 硅片集成的核心是硅通孔 (TSV) 技术 , 用于互连堆叠的芯片 , 从而增强性能 , 缩短信号传输时间 , 解决信号延迟等问题。

图 9 (网络版彩图) 3D 先进封装典型结构示意图

4.3.2、三维异质异构微组装技术

异质芯片集成扇出型技术是有别于片上系统和晶圆级封装的先进技术 , 重点通过晶圆再造和再布线技术实现异质芯片的集成 , 解决异质芯片间的高密度互连 , 是实现天线阵列微系统功能模块集成的关键技术 。

采用异质芯片集成扇出型技术是通过半导体先进工艺 , 将不同光、电、磁等功能的异质芯片整合集成再造成一个晶圆 , 并通过薄膜高密度布线 , 形成具有多功能芯片的集成技术 . 可以达到减小天线阵列微系统功能模块厚度和体积的要求 . 异质芯片扇出晶圆级封装 (FOWLP) 厚度小、成本低 , 不需要基板 , 不需要在晶圆上打凸点、回流倒装焊以及助焊剂清洗 , 改善了电性能和热性能 , 更易于系统级封装。

三维异构微组装技术是在多学科系统设计和微纳集成制造工艺的基础上 , 实现不同材料、结构、功能元件的一体化三维异构混合集成 , 解决异构材料的机电、热、力等失配、同时解决并完善系统功能的新型微组装技术 。

从科学研究的层面 , 需要研究半导体工艺的局限性及混合集成的攻关方向 , 例如 , 哪些类芯片、结构体、材料可以进行混合集成 , 哪些类不行 , 并提炼出普适性规律与方法 .从技术研究的层面 , 是在系统架构的基础上 , 通过微焊互连和微封装等混合集成技术 , 将高集成度的 IC 器件、微结构及其他元器件三维组装到封装体内 , 构成高密度、高可靠天线阵列微系统功能模块 , 是实现芯片功能到系统功能的桥梁 。

4.3.3 高密度异质多层基板技术

天线阵列微系统的研究通常是基于三维异构混合集成技术 , 典型是多芯片组件 (MCM) 和系统级封装 (SiP) 技术 . 进一步来说 , 以上技术大多数都是采用叠层型 (MCM-L) 、沉积薄膜型 (MCM-D) 和共烧陶瓷型 (MCM-C) 互连基板技术。

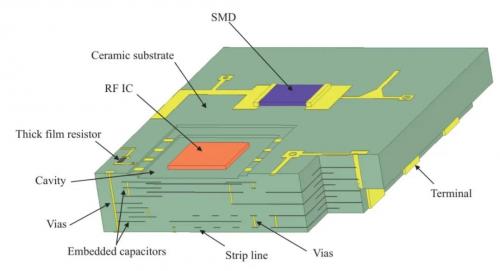

高密度异质多层基板研究是将基板制备技术、膜集成技术 , 通过多层基板协同设计和多物理场耦合分析 , 采用合理的工艺方法进行匹配兼容 , 可制备内置阻容元件和感性元件的高密度无源集成异质多层基板或集成无源器件 (integrated passive device, IPD). 厚薄膜无源元件集成基板技术是采用先进微电子技术和材料 , 在 LTCC 多层基板内置电阻、电容、电感等元件 , 如图 10 所示 , 可缩短分立器件的互连长度 , 降低寄生效应 , 减少互连焊点 , 同时有利于解决多径衰弱、频谱拥挤、噪声干扰等系统问题 。

图 10 (网络版彩图) 基于 LTCC 多层基板内置无源元件集成示意图

混合多层基板是两种或两种以上不同材质的基板集成制作为多层基板 , 基于不同材质基板的物理参数和特性 , 进一步提高多层基板的性能和布线密度、组装效率 , 降低成本 . 例如 , 共烧陶瓷 / 薄膜型混合基板 , 其中薄膜多层基板可布置高速信号线、接地线和焊接区 , 充分利用薄膜多层布线的信号传输延迟小、布线密度高的特性 , 共烧陶瓷基板上布置电源线、接地线或低速信号线 , 充分利用它易于实现较多布线层数和适宜于大电流的特性。