NCO 64位相位累加器本身在执行时,就用到了双精度2的小数格式的SHARC 32位ALU。提供存储器更新的整个相位累加器执行过程需要11个核心周期,因此,每个NCO输出样本都在约33个核心周期内生成。

图4中的框图显示了基于软件DSP的NCO的功能模块实现方案,每级都参考了运算格式精度。此外,进行信号模拟重构以及实现完整的DDFS还需要用到一个或两个DAC及其模拟抗混叠滤波器电路。处理链的关键元件包括:

u 64位相位累加器(SHARC ALU双精度,带溢出);

u 64位小数定点到40位浮点转换模块;

u 范围缩减模块[0至+ π/2]和象限选择(Cody和Waite);

u 正弦逼近算法(Hart),用于相位-幅度转换;

u –1.0至+1.0范围内的sin(x)重构和归一化级;

u LP FIR滤波器和sin(x)/x补偿(如果必要);

u 以及40位浮点至D位定点转换和标度函数,以匹配DAC数字输入。

可以在NCO输出端放置一个可选的数字低通滤波器,以去除可能进入目标频段的杂散和噪声。或者,该滤波器可以提供插值和/或逆sin(x)/x频率响应补偿,具体由选择用于模拟重构的DAC决定。这种低通FIR滤波器可以使用MATLAB Filter Designer工具设计。例如,假设采样频率为48 kSPS,带宽为DC至20 kHz,带内纹波为0.0001 dB,带外衰减为-150 dB,则可以实施具有40位浮点系数的高质量均衡纹波滤波器。它只有99个滤波系数,在单指令单数据(SISD)单计算单元模式下,总执行时间将消耗约120个SHARC核心周期。经过数字滤波后,使用其中一个DSP同步串行端口,由DMA将计算的样本对发送至DAC。为了获得更好的速度性能,链接DMA操作也可以使用大型乒乓存储器缓冲区来支持块处理操作。例如,块数据大小可以等于FIR数据延迟线的长度。

为了实现最佳SFDR,在NCO上进行的最后调整

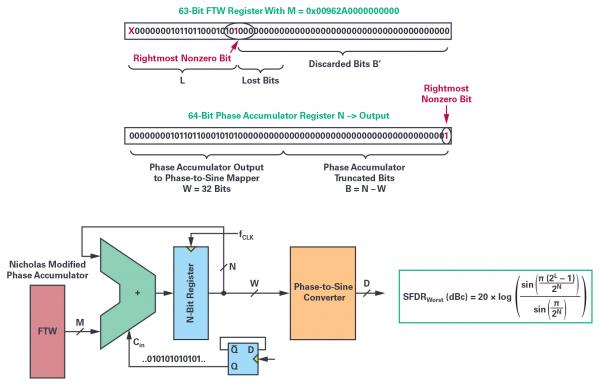

如前所述,NCO遭受杂散的主要原因是对相位累加器输出的截断,其次是针对通过计算或列表得出的正弦值的幅度量化。相位截断引起的误差通过相位调制(锯齿形)在载波频率附近产生杂散,而正弦幅度量化引起与谐波相关的杂散,不过长期以来一直被认为是随机误差和噪声。如今,在Henry T. Nicholas和H. Samueli撰写的技术论文7中,从数学角度深入阐述了相位累加器的操作。在深入分析的基础上,提出了一种模型,将相位累加器视为分立式相位样本排列生成器,并据此预测频率杂散。无论相位累加器参数(M、N、W)是多少,相序的长度都等于

![]()

(其中GCD是最大公约数),如图4所示,由频率调谐字M最右边的位位置L决定。因此,L的值定义序列类别,这些类别彼此共享自己的相位分量集,但根据

![]()

比率重新排序。这些在时域内生成的截断相位样本序列被用来通过DFT确定频率域内各杂散线各自的位置和大小。这些序列还表明,M (FTW)的奇数值显示最低频率杂散的幅度,并建议对相位累加器进行简单的修改以满足这些最低程度的条件(只需在FTW中添加1 LSB)。如此,相位累加器的输出序列必须始终具有相同的2N个相位元素,无论相位累加器的M值和初始内容是什么。之后,最差的杂散信号音幅度等级降低3.922 dB,等于SFDR_min (dBc) = 6.02 × W。由Nicholas更改的相位累加器为NCO提供了多种优势,首先,它消除了FTW最右边的位非常接近MSB(FMCW应用中的频率扫描)的情况,其次,它让杂散幅度与频率调谐字M无关。这种修改可以通过按采样速率fS切换ALU LSB来轻松实现,如果FTW LSB置位至逻辑1,则可以仿真与相位累加器相同的行为。相位累加器大小N = 64位时,对于所需频率FOUT的精度,可以将LSB偏移视为可忽略的误差。

图5.FTW最右边非零位的位置确定了理论上SFDR的最差水平。由Nicholas修改的相位累加器解决了采用任何N值的问题,并且使NCO的SFDR最大。

采用32位输出相位字W时,由相位截断导致的最大杂散幅度会限制为–192 dBc!正弦采样值的有限量化也会导致产生另一组频率杂散,该杂散通常被认为是噪声,可采用大家熟知的SNRq(dB) = 6.02 × D + 1.76公式进行估算。这必须添加到寄生参数中,因为相位-正弦幅度转换算法阶段的近似误差被认为是可以忽略的,但是,必须非常谨慎地选择相位-正弦近似算法和计算精度。

这些结果表明,从理论水平上,我们的软件正弦NCO的线性和噪声都远远超过了测试市场上大多数高精度ADC所需的阈值。它仍然需要找到信号链中最后一个、也是最关键的元件:重构DAC及其互补模拟抗混叠滤波器和相关的驱动电路,以满足预期的性能水平要求。

重构DAC:关键之处!

首先可能会选择具备出色的非线性误差(INL和DNL)规格的高精度DAC,例如出色的20位高精度DACAD5791。但是它的分辨率只有20位,而且其R-2R结构不支持实施信号重构,特别是产生非常纯的正弦曲线,这是因为在输入代码转换期间,它存在很大毛刺。传统的DAC架构基于二进制加权电流发生器或电阻网络构建,对数字直通和数字开关损伤(例如外部或内部时序摆动),以及数字输入位的其他开关不对称非常敏感,特别是在会导致能量变化的重大转变期间。这就产生了与代码相关的瞬态,从而产生高幅度谐波杂散。

在20位以上的分辨率下,使用外部超线性快速采样和保持放大器对DAC输出去毛刺并无太大帮助,这是因为它在几十LSB下会生成自己的瞬态,且会因为重采样产生组延迟非线性。信号重构主要存在于通信应用,通过使用分段架构(混合适用于MSB的完全解码部分和适用于最低有效位的二进制加权元件)来解决毛刺问题。遗憾的是,目前还没有超过16位精度的商用DAC。与NCO完全可预测的行为不同,DAC误差难以预测和准确仿真,尤其是当制造商的动态规格很小或者不存在时,但专用于音频应用的DAC或ADC除外。插值过采样和多位∑-DAC似乎是唯一的解决方案。这些先进的转换器具有高达32位的分辨率、超低失真和高信噪比,是在中低带宽内实施信号重构的最佳选择。为了在音频频谱或稍宽的频段(20 kHz或40 kHz带宽)内实现出色的噪声和失真性能,可以使用ADI公司产品系列中杰出的∑-DAC产品,音频立体声DACAD1955, 虽然分辨率最高为24位,这款DAC仍然是市场上非常受欢迎的音频DAC。

这款音频DAC于2004年推出,基于多位Σ-Δ调制器和过采样技术,配合各种技巧,用于缓解这种转换本身固有的失真和其他问题。8

即使目前,AD1955采用的插值LP FIR滤波器仍然是同类出色产品。它具有极高的阻带衰减(≈–120 dB)和极低的带内波纹(≈±0.0001 dB)。它的两个(左侧和右侧通道)DAC可以以最高200 kSPS速度运行,但在48 kSPS和96 kSPS时实现最佳交流性能,其动态范围以及立体声模式下的SNR,都支持典型的EIAJ标准、A加权120 dB系数。在单声道模式下,两个通道同时异相组合,性能有望提高3 dB。但是,对于宽带应用,这些规格不太实际,这是因为它们是合成的,带宽范围在20 Hz至20 kHz之间。带外噪声和杂散不会超过20 kHz,部分是因为EIAJ标准、A加权滤波器和音频行业规格定义。这种满足特定音频测量要求的带通滤波器模拟人耳的频率响应,与未滤波的测量值相比,性能提高3 dB。