本文重点介绍近些年微波电路设计取得的进步,这意味着现在采用硅芯片技术中的低相位噪声 VCO 可以覆盖一个倍频程范围。

多年来,微波频率生成使工程师面临严峻的挑战,不仅需要对模拟、数字、射频(RF)和微波电子有深入的了解,尤其是锁相环(PLL)和压控振荡器(VCO)集成电路组件方面,还需要具备可调滤波、宽带放大以及增益均衡等专业知识。

本文重点介绍近些年微波电路设计取得的进步,这意味着现在采用硅芯片技术中的低相位噪声 VCO 可以覆盖一个倍频程范围。在这样的 IC 上集成输出分频器可以支持几个低频倍频程范围,输出集成倍频器则支持单个 IC 生成高达 32 GHz 的频率。随着小数 N 分频 PLL 频率合成器技术的进步,现在微波频率范围 rms 抖动可低至 60fs,具备无限小的频率分辨率和极小的杂散信号。低插入损耗宽带滤波器可以和这些集成 PLL/VCO IC 配合使用,以提高整个系统的频谱性能,大大降低了微波和毫米波本地振荡器带来的相关挑战。

简介

本地振荡器(LO)是现代通信、汽车、工业和仪器仪表应用中的关键组件。无论从基带到 RF 实施上变频还是反过来的下变频,为汽车雷达、材料检测应用生成扫频,或者为上述应用电路的构建和测试而开发仪器仪表,我们生活的很多方面都存在 LO。电路和工艺技术的进步已帮助降低了此类电路的成本、复杂性和面积;与过去需要更广泛地混合使用有源和无源技术相比,现代集成电路大大降低了 LO 的设计难度。

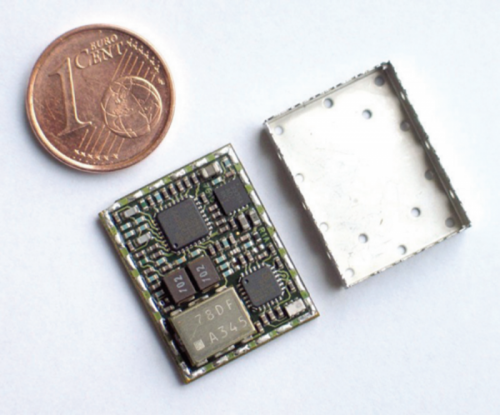

过去,适用于 GSM 等 2G 通信应用的大部分 LO 都使用与 ADI 公司的 ADF4106 类似的整数 N 分频 PLL,以及窄带 T 封装 VCO(例如 VCO190-1846T)。在大多数情况下,这些 VCO 的高品质因素(Q)使其非常易于满足该严苛标准下的相位噪声规格。那时的手机一般只支持一种无线标准,标准本身的数据速率也有限(虽然 2G 网络出色的覆盖率帮助手机获得了广泛的市场认可)。基站 LO 一般是使用多种 IC 和 VCO 子模块组合而成的模块,如图 1 所示。

图 1. 适用于无线通信的 LO 模块。

对无线数据速率以及与不同的全球无线标准兼容性的需求不断提高,促进了宽带 VCO 的发展,与窄带 VCO 相比,宽带 VCO 有助于实现更宽的频率覆盖范围,支持更多的新可用频谱。支持这种数据吞吐量的微波回程网络也承受着压力,需要支持高阶调制率,可针对不同范围和标准进行配置,同时帮助网络提供商降低工程难度,提高投资回报率。为了支持这些网络开发,典型的信号分析仪使用了庞大笨重的钇铁石榴石(YIG)振荡器,以及使用类似技术的笨重滤波器。

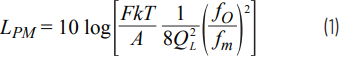

VOC 改进

开发集成硅芯片微波 VCO 面临的最大技术挑战是可用晶圆制造工艺中的 Q 值有限。在许多情况下,绕线电感(用于 T 封装 VCO 中)的 Q 值可能从数百的典型值降至刚刚超过 10,因 Leeson 方程的限制,Q 值会严重影响相位噪声,根据此方程,相位噪声 LPM(公式 1)与 VCO Q 值成平方反比,和输出频率成平方正比关系。

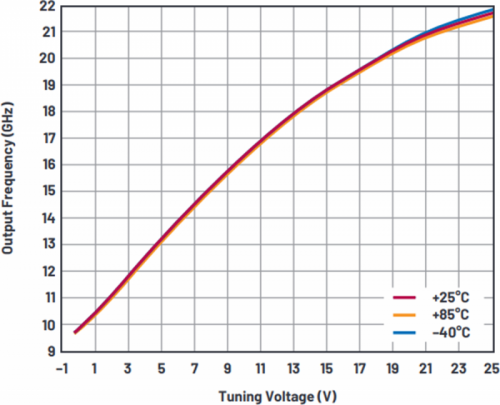

基于砷化镓(GaAs)或锗硅(SiGe)制造的宽带单核 VCO 通过将 VCO 的调谐端口范围从 5V(大部分硅基 PLL 电荷泵可用的典型电压)扩展至 15V、甚至 30V 来解决范围与噪声的问题。这意味着,谐振器 Q 可以保持不变,但扩展的变容二极管可调谐性可以提供更广泛的调谐范围,但不会恶化相位噪声。这种更高调谐范围带来的挑战,可以通过使用有源低通滤波器以将电荷泵电压(典型值为 5V)转换为 15 V 或 30 V 来解决(参见图 2 中 HMC733 的调谐范围)。这些有源滤波器需要使用高压低噪声运算放大器。所以,典型的微波 LO 将由 PLL(如 ADF4106),运算放大器以及 GaAsVCO 组成,在很多情况下,还需要一个外部分频器,将 VCO 信号分频至 PLL 允许的最大输入频率(对于 ADF4106,为 6 GHz)。GaAs VCO 一般在 S 频段和更高频段下运行,因为谐振器电路一般在 2GHz 以上提供最佳性能。设计电路板时更要格外小心,这需要熟知电源、模拟以及 RF 和微波领域专业知识。PLL 滤波器的设计及其性能仿真都需要具备丰富的控制理论和噪声建模经验,并且需要熟悉每个组件。完成这些任务所需的经验并不容易获得,一般只有从事硬件设计工作几十年的资深人士才具备。

图 2. HMC733 调谐范围。

目前有多种技术可以解决低 Q 值问题。在类似 ADF4360 的产品系列中,裸片(粘接到焊盘上)表面焊线的 Q 值大约为 30。厚金属电感也可以改善 Q 值,改进变容二极管 Q 也有助于大幅提高谐振器 Q 值,从而进一步改善相位噪声性能。适合制造高频率 VCO 和 N 分频器电路的 BiCMOS 工艺,以及用于开关各种电容的 CMOS 逻辑电路,这些意味着宽带 PLL 和 VCO IC 切实可行,其小巧的尺寸和更宽的频率范围则使其迅速得到无线市场的认可。

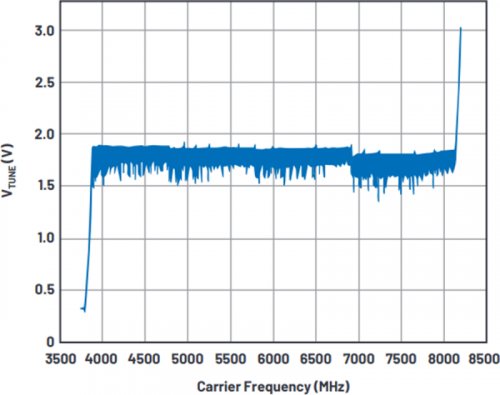

许多宽带 LO 都采用了这种方法。覆盖整个倍频范围的 VCO 很有优势,这是因为一组分频器可生成的频率范围只受最低可用 VCO 频率和最高可用分频比限制。采用硅芯片工艺的 VCO 设计取得了重 大突破,通过开关不同的电容组,可以将 VCO 范围划分为多个子频段。这支持实现更广泛的频率覆盖范围,无需通过降低振荡器谐振器 Q 值来牺牲相位噪声,同时支持使用电压较低的电荷泵,所以无需使用额外的运算放大器,其需要更高的电源电压轨。进一步改善可将 VCO 频段的数量从数十个增加到数百个,甚至在单片 IC 上开发其他单独的重叠 VCO 内核(按需进行开关),从而进一步优化相位噪声,例如 ADF4371(图 3)。从图 2 中 HMC733 的单核 VCO 与图 3 的 ADF4371 的多频段 VCO 之间,可以看出明显的不同。

图 3. ADF4371 频率与 VTUNE 的关系。

从图 2 的频率与 VTUNE 关系图中可以看出,HMC733 调谐电压与输出频率成正比,而在图 3 中,调谐电压基本上在 VTUNE 的 1.65V 目标值的几百毫瓦以内。智能频段选择逻辑或自动校准电路意味着用户无需针对频率开发频段查找表,且存在足够裕量,可以保证在电源电压范围,尤其是温度电压范围内可靠运行。