ADF4371VCO 的基波频率范围为 4GHz 至 8GHz,这是考虑了制造设备所使用的 SiGe 工艺的 VCO 相位噪声性能的最佳点。为了生成更高频率,我们使用了倍频器。通过重新设计 VCO 来实现双倍频率范围存在一定问题,因为噪声的降低幅度高于通过扩展 VCO 的频率范围所预期的 6dB。所以,采用了倍频器,它将 VCO 范围从 8GHz 扩展到 16GHz,还采用了四倍频器,将 4GHz 至 8GHz 的 VCO 范围扩展到 16GHz 至 32GHz。在每种情况下,倍频器都会带来一些频率噪声,包括 VCO 馈通,以及 2×、3×和 5×VCO 频率。为了降低滤波要求,每个倍频器电路都包含跟踪滤波器,以调谐输出,最大限度提高了所需频率与频率噪声的功效比。双倍输出的次谐波抑制一般低至 45dB,四部输出则低至 35dB。

宽带工作

从之前所示的窄带示例中,可以看出新型 PLL/VCO 技术优势明显,但与使用 HMC733VCO 的 HMC704PLL 生成宽带频率相比,使用 ADF4371 还可以更进一步改善。用户使用分立式解决方案时面临诸多挑战,其目标是生成 20GHz 至 29GHz 的干净可变 LO。

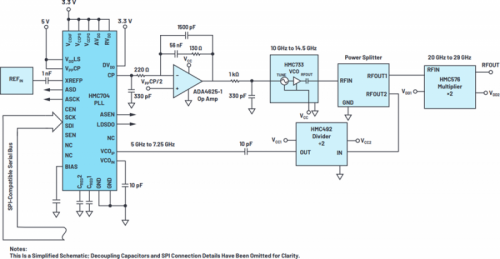

首先,HMC733VCO 的输出功率必须在板上分配,并分频至适合 HMC704 的频率,所以必须使用外部分频器(如(HMC492),将 10GHz 至 14.5GHz 范围分频至 HMC704 允许的 5GHz 至 7.25GHz。

然后,必须使用倍频器(如 HMC576)将 10GHz 至 15GHz 频率范围倍增至 20GHz 至 30GHz。

需要使用有源低通滤波器来生成 HMC733 所需的调谐电压。本示例使用 ADA4625-1。这也要求运算放大器的电源电压高到足以生成所需的调谐调压(在本例中,为 15 V)。

调谐灵敏度的变化必须在整个 VCO 频率范围内进行补偿。这通常通过调节电荷泵电流,以保持电荷泵增益和 VCO 增益的乘积来实现。

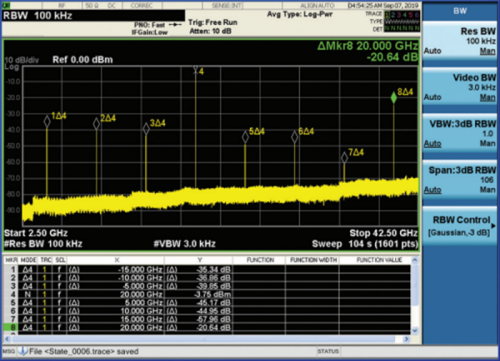

HMC576 倍频器之后的 VCO 馈通约为–20dBc。ADF4371 的调谐滤波器会将倍频器产生的不必要的频率抑制在 35 dBc。这大大简化了后续滤波。

图 8. 分立式 PLL/VCO 倍频器解决方案。

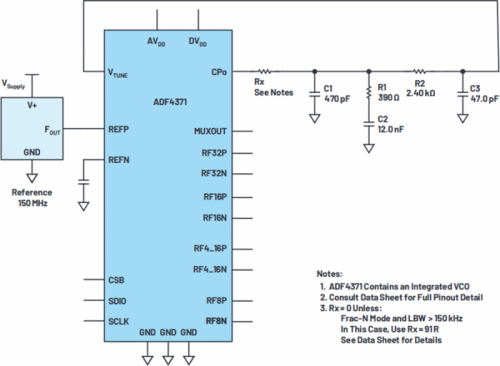

相比之下,ADF4371 PLL/VCO 开箱即用,只需使用一个高品质的外部参考频率源,即可生成此频率。可以复制 EV-ADF4371SD2Z 的布局,同时复制相应的电源管理解决方案。环路滤波器的设计也会明显简化,因为不需要最终用户补偿灵敏度(kV)的变化,也无需使用有源滤波器元件。用户无需花费数周时间来选择器件,也无需花费大量时间来为每个分立式组件构建仿真模型,他们可以直接使用 ADIsimPLL 来设计和仿真预期的性能,并通过 ADF4371 评估板来评估获取准确的预期结果,因为评估结果与仿真性能非常接近。更少的组件数量和更高的集成水平能够大幅改善系统的尺寸和重量,此外,也会大幅改善系统性能,计算得出的 ADF4371 集成 rms 抖动为 60fs,而分立式解决方案的抖动为 160fs。从图 9 可以看出,组件数量和电路板面积均明显节省,如果不包括必要的退耦电容和其他所需的无源器件,有源器件和功率分路器的总面积相当于 96mm2,而 ADF4371 仅 49mm2。用户也可以根据需要为 VCO 选择 3.3V 电源,以节省功率。

图 9. ADF4371 框图。

在基波 VCO 模式下,ADF4371 的频谱纯度达到最高,无用杂散(非带内)仅限于 VCO 谐波。对于许多转换器时钟应用,方波本身的特性不会造成问题,可能确实合乎需要,但对于仪器仪表应用来说,宽带杂散频率一般必须低于 50dBc。可调谐波滤波器可帮助消除这些谐波,专门设计的 ADMV8416/ADMV8432 非常适合对 ADF4371 的输出进行滤波。

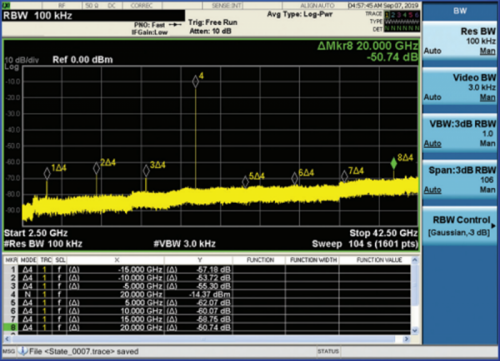

ADMV8432 是一款可调谐带通滤波器,指定中心工作频率范围为 16GHz 至 32Ghz,典型 3dB 带宽为 18%,典型插入损耗为 9dB,宽带抑制大于 30dB,专为配合 ADF4371 四倍频器输出使用而设计。ADMV8416 也是一款可调谐带通滤波器,工作频率范围为 7GHz 至 16GHz,典型 3dB 带宽为 16%,典型插入损耗为 8dB,宽带抑制大于 30dB,可配合 ADF4371 倍频器输出使用。

图 10. ADF4371 20 GHz 输出。

图 11. 使用 ADMV8432 滤波器的 ADF4371 20 GHz 输出。

ADMV8416/ADMV8432 均采用双重叠频段结构,带内部 RF 开关,可以实现更宽的频率覆盖范围,同时保持出色的抑制性能。频段选择通过对所需的电平转换器实施数字逻辑控制来实现。电平转 换器确保内部 RF 开关会进行相应的偏置,以获得高于+34dBm 的最佳输入三阶交调截点(IIP3)。

在每个工作频段内,可调谐滤波器通过 0V 至 15V 的模拟控制电压进行控制,消耗的电流不到 1µA。这种控制电压一般通过 DAC 和运算放大器驱动电路生成。例如 AD5760DAC 后接 ADA4898 运算放大器,可以为滤波器提供相对较快的调谐速度和低噪声驱动电压。如果调谐速度不太重要,则可以将 DAC 直接驱动至滤波器的调谐端口。

考虑到这些模拟调谐滤波器的性能指标,可以在牺牲少量输出功率的情况下,去除 ADF4371 频率合成器倍频器和四倍频器输出中的无用谐波成分。虽然为了解决插入损耗问题,可能需要额 外的放大级,但滤波器一般比分立式开关组解决方案要小,尤其在需要宽带可调谐性的情况下。此外,频率合成器的杂散电平在滤波前一般为–35dBc,滤波后可以达到–55dBc。未滤波且 未使用的输出的耦合可能会影响馈通,构建模型时应该非常小心,以实现滤波器 IC 的全阻带抑制。

结论

随着相关工艺、电路和封装技术的各种创新,频率生成技术不断发展,能够为用户提供比以前的分立式解决方案的体积更小、功能和性能更出色的解决方案。宽带频率工作趋势推动了新款 IC 的开发,即覆盖多个倍频率,频率范围高达 32GHz。宽带 PLL/VCO 提供了很高的灵活性和简洁性,可以帮助最终用户大幅缩短设计时间和加快上市时间。

对频谱纯度的需求推动滤波 IC 不断创新,这些 IC 与新开发的频率合成器 IC 配合使用,可以提供现代无线应用所需的低相位噪声和高频谱纯度毫米波信号源。用户可以使用免费的仿真工具 ADIsimPLL 来评估和比较 PLL 性能,还可以使用简单易用、具有直观界面的快速行为模型帮助进行组件选型。这款工具为设计工程师节省了大量时间,使他们无需构建大量不同领域的数学模型来预测性能。