在演算法交易领域的最新进展是导入一些更低延迟的解决方案,其中最佳的方式是使用FPGA搭建的客制硬体。这些FPGA硬体可说是硬编码ASIC的极致性能和CPU的灵活度之间的桥梁,提供大量的资源且可加以配置,使其得以较软体解决方案更大幅缩短往返交易延迟。

高性能运算对于许多应用至关重要。在其中一些最竞争的应用领域,开发人员经常能为其嵌入式系统问题找到解决方案。例如,高频交易(HFT)是一种演算交易的形式,其交易量占美国证券交易量的绝大部份。高频交易使用机器学习演算法处理市场资料、拟定策略,以及在几微秒的时间内执行订单。

为了获得每次交易中哪怕只有几分之一美分的利润,高频交易员以很高的交易量短期进出交易所。使用HFT演算法的系统持续监测价格波动情况,以利于调整短线交易策略。由于这是非常短期的交易策略,HFT企业无需耗费大量资本、累积头寸或隔夜持有其投资组合。目前,高频交易量占美国证券交易量的75%。

在21世纪初,HFT交易侧重于优质的演算法和交易策略。现在,由于最普及的几种系统仅存在几秒的延迟,决胜的关键不再是速度,而是策略。到了2010年,由于演算法的进展已不足以获得交易优势,为了战胜彼此,参与者开始缩短tick-to-trade的交易延迟,从而使交易时间缩短至数微秒。

在次毫秒级买卖交易订单的刺激下,HFT平台开始了一场竞争激烈的速度竞赛,以便将市场资料的往返延迟缩短至微秒级。由于仅仅几奈秒的差别往往带来巨大的‘潜伏套利’竞争优势(或称为‘抢先交易’),交易企业一直在寻找更快的交易伺服器。

采用软体途径处理订单

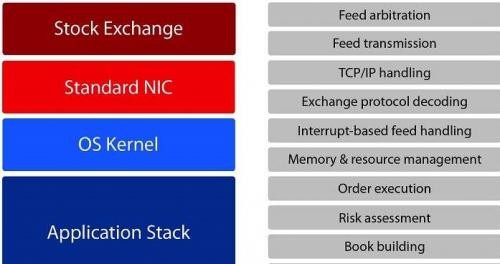

传统上,HFT交易一向使用软体工具。这些工具利用了高性能运算系统,能够高效地执行复杂的交易策略(图1)。这些系统中的作业系统核心控制对其CPU和记忆体资源的存取,而应用堆叠则负责处理所有的交易策略,由网路介面卡(NIC)连接系统至证券交易所。

图1:采用软体途径处理订单的配置(来源:Cypress)

然而,这种配置存在交易延迟的缺点:

标准NIC并未专为处理TCP/IP和专用交易协定进行最佳化,而且无法板载处理市场资料馈送

主系统和乙太网路(Ethernet)卡之间的PCI Express汇流排会增加数微秒的延迟

核心OS原生的基于中断途径就会导致较长的延迟

这些解决方案基于共享记忆体资源的多核心处理器。在处理来自证券交易所的资料馈送时时,确定性延迟至关重要,存取共用记忆体绝不是一个最佳方式

在演算法交易领域的最新进展是导入了一些更低延迟的解决方案,其中最佳的方式是使用现场可程式逻辑闸阵列(FPGA)搭建的客制硬体。这些设备可说是硬编码ASIC的极致性能和CPU灵活度之间的桥梁。透过FPGA提供大量的资源且可加以配置,使其得以较软体解决方案更大幅缩短往返交易延迟。

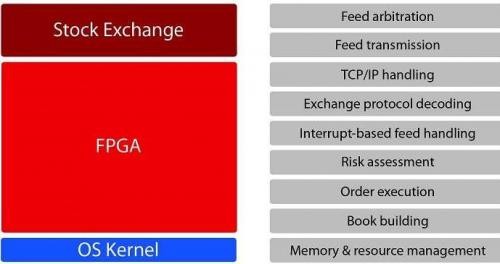

采用FPGA途径处理订单

除了灵活之外,FPGA还可以进行编程设计,以便自行处理资料撷取、风险评估与订单处理等关键任务。这种自给自足的特性使其较软体演算法更快、更可靠。让基于FPGA的解决方案能够大幅提升电子交易性能的关键因素是:它们能让过去由软体处理的过程直接在FPGA上进行。

图2:采用FPGA途径处理订单的配置

相较于软体演算法,FGPA的配置具有这些优势,原因就在于以下的功能被分流到FPGA:

处理TCP/IP讯息

解码FAST或类似的交易专用协定,以及撷取相关资料

进行交易决策,而不至于导致任何基于核心的中断延迟

透过管理FPGA中的订单簿(order book)和交易记录以降低风险

凭藉着这些优势,基于FPGA的解决方案能够提供超低延迟的资料馈送处理功能,以及更快的订单执行和风险评估速度。它们还能实现最高的每瓦功耗性能,尽可能地降低能耗和热量要求。FPGA解决方案的另一个优势是透过扩展部署‘FPGA现场’配置的能力。

组成基于FPGA途径关键之一在于巧妙地整合4倍资料率(QDR)记忆体,实现确定性记忆体存取速率以及经过最佳化的VHDL程式码。在FPGA的记忆体中需要维护的两个最重要资料集是用于维护订单簿的证券资讯和用于分析风险的资料与时间戳记。二者均对快取记忆体提出了不同的要求。资料封包的资料与时间戳记对于保存交易决策的准确记录、重现过去的事件非常重要。这些记录所需的精密度达数十奈秒,这使得记忆体延迟(即为记忆体提供位址以及从资料汇流排取得资料之间的时间延迟)更加至关重要。