LPDDR的运作

LPDDR4功能本质上包含四项基本操作:启动、读取、写入和预充电。这些操作的其他变异形式,如突发读取/写入和自动预充电等,可能构成一个更长的指令列表,但并不至于带来新的技术挑战。此外,它还添加了刷新、训练和模式缓存器作业等维护性指令,以因应复杂的操作命令。

这些基本的操作简要介绍如下: 启动: 在内存数组中选择特定字符线(wordline),即可“开启”一个分页。该分页上的内容将会被感测到并进行锁存,然后保持开启以用于在读取作业时进行回写,或在“读取-修改-写入”作业时被再次写入。 读取: 开启读取数据序列,每个burst内存群组的数据会从感测放大锁存中被加载到DDR缓存器中。紧接着DDR缓存器开始依序读取,每次读取一个16bit字。同时,芯片透过隐藏缓存器在仍保持开启状态的分页上进行回写。 写入: 数据被加载DDR缓存器,每次一个16位字。数据随后被转移到隐藏缓存器中,待分页开启时写入数据。当进行写入时,DDR缓存器可依需要同时加载新的256位数据,等待下一次写入。 预充电: 在最后一个burst内存群组被读取或写入后,内存数组必须为下一次操作做好准备。在写入情况下,必须等待一个写入恢复延迟,以确保最后的burst群组可在继续其他操作前被成功写入。这时,开启的分页已被关闭,使位线能够自由浮动,并重新充电回到先前提到的VDD/2电位。

值得注意的是,只有启动操作才涉及内存数组感测;读取操作只涉及在锁存感测数据与DDR缓存器之间传输数据,以及读取DDR缓存器的数值。

根据所需的操作序列不同,有些DDR的时序可能极其复杂。但如果相邻读取操作发生在不同内存组的数据之间,则可大幅简化时序。因为在从下一个内存组中读取数据之前,不必在原有的内存组中等待回写和预充电。时序控制最困难的是来自同一内存组的连续读写。

实现内存数组:MAT

理论上,尽管一个内存组的逻辑容量可能达到32K行与16K列,但以现有技术而言,现实上并不可能制造出这样的内存数组。这是因为:

? 驱动器在选择分页时的驱动能力有限;在性能符合规格要求的前提下,只有一定数量的选定晶体管可以被驱动。

? 感测放大只能支持有限数量的储存单元。如果储存单元的数量太多,由于电荷分配造成电压变化减小,而被噪声淹没。

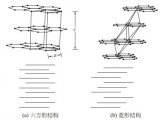

因此,为了确保内存芯片可靠且易于制造,每一种内存应用都存在不同程度的实体尺寸限制。达到这种上限的内存数组被称作“内存数组片”(memory array tile;MAT)。每个MAT都是功能齐全的数组,本身包含字符线和位线的译码以及感测放大器。

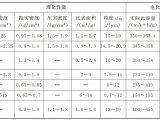

以一种采用2x-nm工艺节点的一般DRAM MAT为例,其位线和字符线的规模分别达到1,024条和620条。字符线的数量并不是2的整数次方,这带来了一些解码方面的挑战。该芯片或许只用了最后的几个MAT,但这是一个可以忽略的芯片建置细节。

透过打造一个16×53大小的MAT数组,可为具有这一尺寸的内存组实现总共848个MAT。一个完整分页整合一行MAT的内存单元:当开启一个分页时,同时启动同一行有MAT内存单元上相应的字符线。

图5:传统DRAM的实体布局

在了解了这些背景知识后,接下来将讨论全新的Kilopass内存单元,以及它如何打造与此相同的储存组。