为了降低功耗,一种关键方法是降低SRAM阵列的最小工作电压Vmin。5nm工艺中增加的随机阈值电压变化限制了Vmin,进而限制了功耗的降低。SRAM电压减小趋势如图4所示,其中蓝线表示没有写辅助的Vmin,红线表示有写辅助的Vmin,显示了每一代写辅助的巨大好处。可以看出,从7nm到5nm的Vmin几乎没有改善,表明必须通过改善写入辅助电路来进一步降低功耗。本文主要介绍两种写辅助方,以实现较低的Vmin工作电压:负位线(NBL,Negative Bit Line)和降低单元VDD(LCV,Lower Cell VDD)。

图4.没有写辅助(蓝线)和有写辅助(红线)的SRAM工作电压随节点变化图。

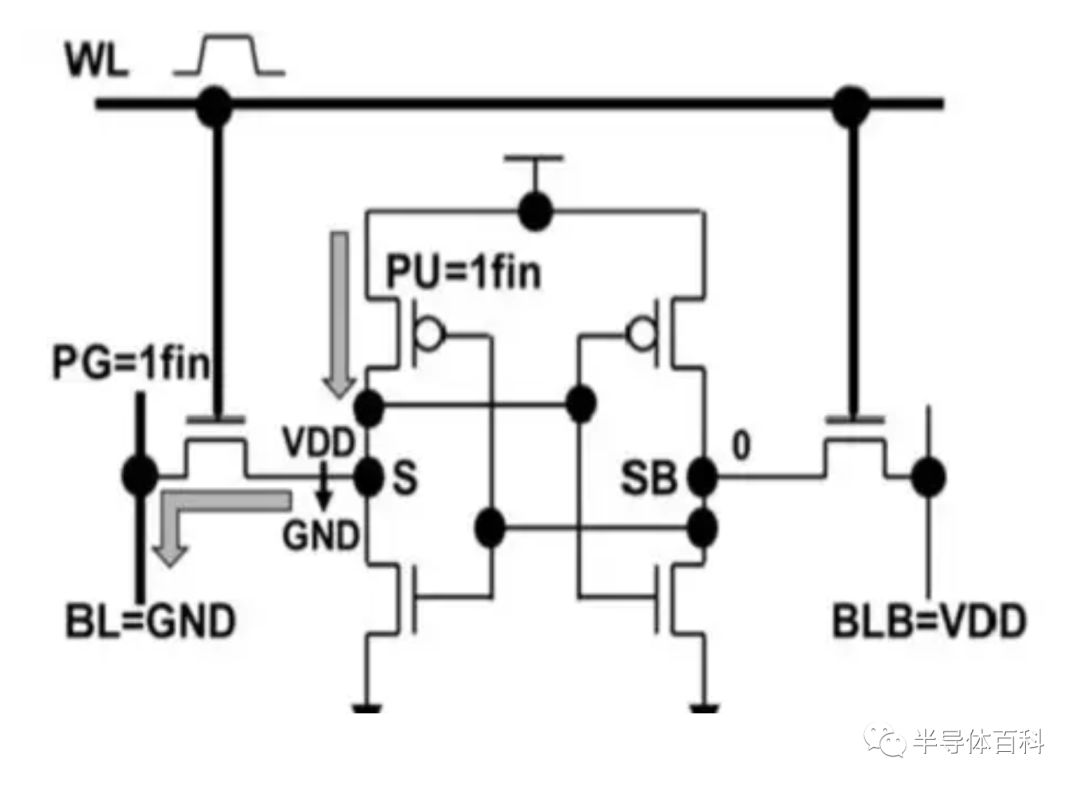

SRAM单元示意图如图5所示,显示了PU与传输门晶体管PG之间在写入操作期间的竞争。采用较强的PU晶体管可以获得较高的读取稳定性,但会显着降低写入容限,并导致写入Vmin问题。

图5. SRAM单元示意图,显示了PU和PG 之间在写入过程中的竞争。

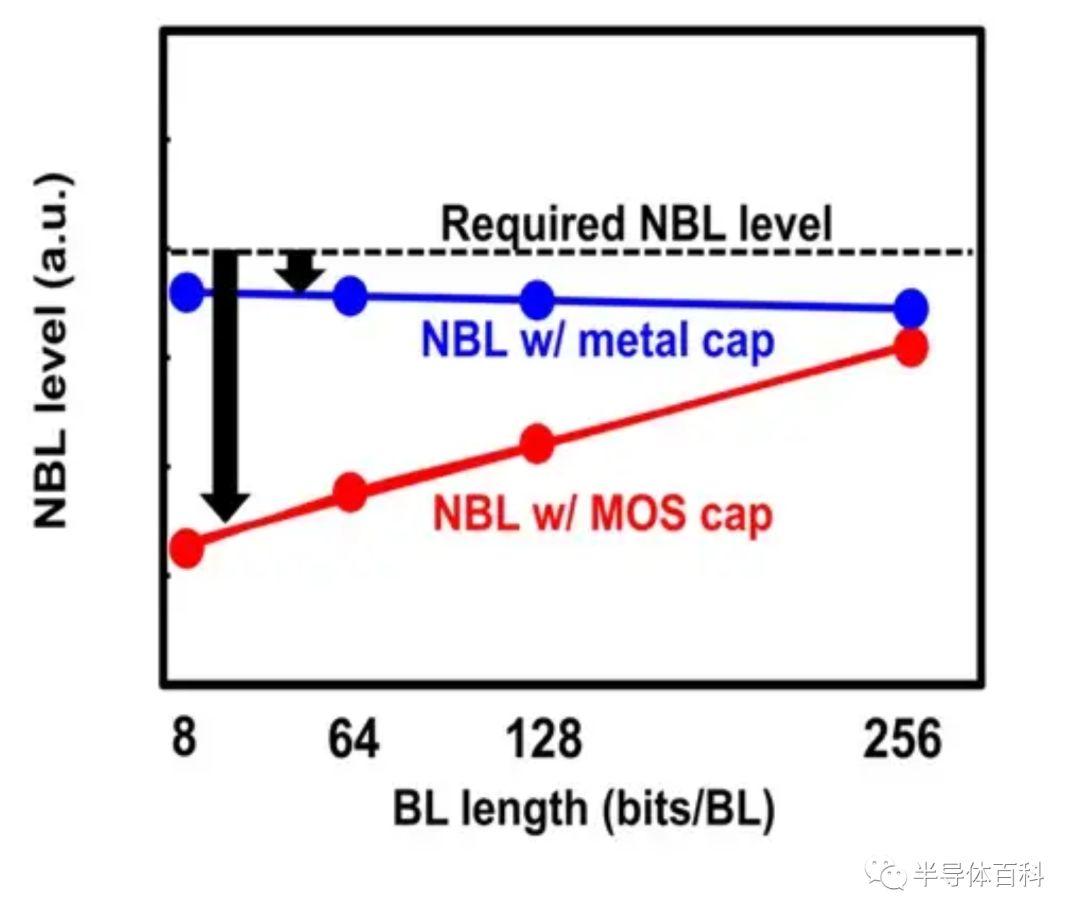

改善写入Vmin的第一种方法是降低写入期间的位线电压,称为负位线电压(NBL)。这种方法业界已经使用了几年,使用MOS电容器在位线上产生负偏置信号,但是这种写辅助电路会导致芯片面积增大。此外,固定数量的MOS电容会在短BL配置中引起过高的NBL电平,并可能导致短位线上的动态功耗过大,如图6所示。

图6.固定数量的MOS电容会在短BL配置中引起过高的NBL电平,并可能导致过高的动态功耗,金属电容器NBL可以避免该问题。

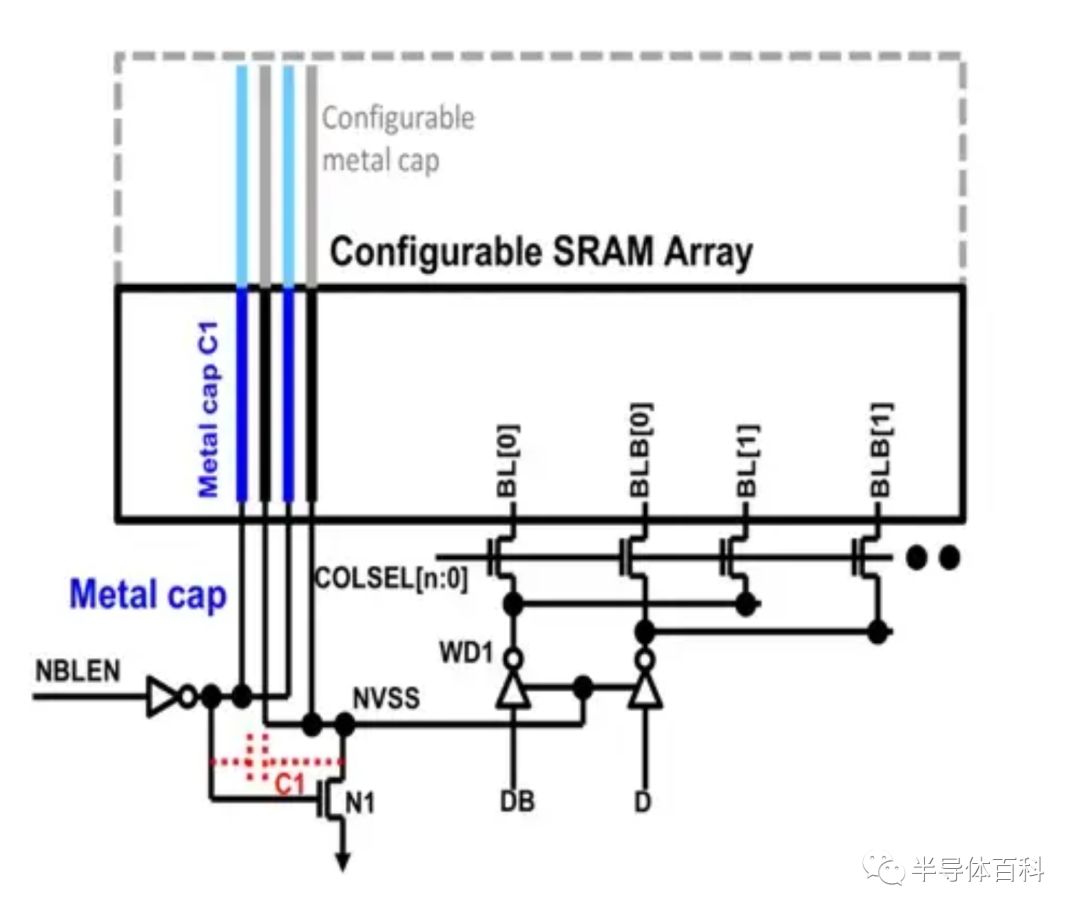

通过基于SRAM阵列上方金属线的耦合金属电容器方案,可以避免过压和MOS电容器面积问题。为避免补偿过量,可以使用SRAM阵列位线长度来调节金属电容器的长度,从而节省动态功耗。此外,还可以调节NBL电平,以补偿远侧存储单元上的由于字线IR下降引起的写入能力的损失。

图7中的NBL使能信号(NBLEN)驱动金属电容器C1的一侧为负,该电容在虚拟电容C1处耦合一个负偏置信号。然后接地节点NVSS,通过写驱动器WD和列多路复用器连到选定的位线。

图7. NBLEN将可配置的金属电容器C1 耦合到NVSS。